# Air Force T. 0. 31S5-4-308-I Army TM 11-5805-663-14-13 Navy NAVELEX 0967-464-0010

TECHNICAL MANUAL

OPERATION AND MAINTENANCE INSTRUCTIONS

PROCESSOR ASSEMBLY (STELMA Part No. 90331023-( AND CORE MEMORY (STELMA Part No. 90331069-(

> STELMA, INCORPORATED F19628-73-C-0014

PUBLISHED UNDER AUTHORITY OF THE SECRETARY OF THE AIR FORCE

15 SEPTEMBER 1975 CHANGE 3 - 1 JUNE 1980 NAVELEX 0967-464-0013 LIST OF EFFECTIVE PAGES

### INSERT LATEST CHANGED PAGES. DESTROY SUPERSEDED PAGES.

NOTE: The portion of the text affected by the changes is indicated by a vertical line in the outer margins of the page. Changes to illustrations are indicated by miniature pointing hands. Changes to wiring diagrams are indicated by shaded arcss.

Dates of issue for original and changed pages are:

Original...0 .. 15 Sep 75 Change....1 .. 1 Jul 79 Change....2 .. 1 Feb 80

Change .. .. 3 ... 1 Jun 80

#### TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS 642 CONSISTING OF THE FOLLOWING:

| Page No. *Change No.                | Page No. *Change No,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page No. *Change No.                                                                                                                                                                                                                                                                                                       |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title $3$ A                         | $5-19 \dots 0$ $5-20 - 5-27 \dots 1$ $5-28 \dots 0$ $5-29 \dots 1$ $5-30 - 5-34 \dots 0$ $5-35-5-36 \dots 1$ $5-37 - 5-43 \dots 0$ $5-44 \dots 1$ $5-45 \dots 0$ $5-44 \dots 1$ $5-45 \dots 0$ $5-52 \dots 1$ $5-53 - 5-51 \dots 0$ $5-52 \dots 1$ $5-56 \dots 1$ $5-56 \dots 1$ $5-57 \dots 0$ $5-58 - 5-60 \dots 1$ $5-61 \dots 0$ $5-61 \dots 0$ $5-61 \dots 0$ $5-64 - 5-66 \dots 0$ $5-67 \dots 1$ $5-68 - 5-73 \dots 0$ $5-74 - 5-75 \dots 1$ $5-68 - 5-75 \dots 1$ $5-76 - 5-80 \dots 0$ $5-81 - 5-85 \dots 1$ $5-86 \dots 0$ $5-81 - 5-85 \dots 1$ $5-86 \dots 0$ $5-94 \dots 0$ $5-109 \dots 1$ $5-112 \dots 0$ $5-113 - 5-117 \dots 1$ | 5-118       -       5-119       0         5-120       1       1         5-121       -       5-133       0         5-134       Blank       0       6-1         6-1       -       0       6-1         6-2       Blank       0       6-1         6-3       -       6-14       0         6-15        0       6-26         6-26 |

| *Zero in this column indicates an o | original page.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                            |

LIST OF EFFECTIVE PAGES

## INSERT LATEST CHANGED PAGES. DESTROY SUPERSEDED PAGES.

NOTE: The portion of the text affected by the changes is indi-cated by a vertical line in the outer margins of the page. Changes to illustrations are indicated by miniature pointing hands. Changes to wiring diagrams are indicated by shaded areas.

Dates of issue for original and changed pages are:

Original...0 .. 15 Sep 75 Change....1.. 1 Jul 79 Change....2 .. 1 Feb 80

TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS 642 CONSISTING OF THE FOLLOWING:

| Page No.                                                                                                                                                                                                                                                                  | *Change No.                                          | Page No.                                                                                                                                          | *Change No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page No.                                                                                                                                                                             | *Change No,                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Page No.         Title         A         i         x Blank         x i         1-0         1-1 - 1-3         1-4         1-5         1-6         1-8         1-9         1-13 - 1-25         1-26 Blank         2-1 - 2-3         2-4 Blank         3-1         3-2 Blank | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | Page No.<br>5-195-27<br>5-20-5-27<br>5-285-295-30-5-34<br>5-37-5-365-37-5-43<br>5-445-455-51<br>5-465-51<br>5-525-55-55-5-55-5-5-5-5-5-5-5-5-5-5- | 0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1 <td< th=""><th>Page No.<br/>5-118 - 5-1<br/>5-120<br/>5-121 - 5-1<br/>5-134 Blank<br/>6-1<br/>6-2 Blank<br/>6-3 - 6-25.<br/>6-26<br/>6-27 - 6-44<br/>Index-1 - I<br/>Index-4 Blank<br/>R-1 - R-9<br/>R-10 Blank.</th><th><math display="block"> \begin{array}{cccccccccccccccccccccccccccccccccccc</math></th></td<> | Page No.<br>5-118 - 5-1<br>5-120<br>5-121 - 5-1<br>5-134 Blank<br>6-1<br>6-2 Blank<br>6-3 - 6-25.<br>6-26<br>6-27 - 6-44<br>Index-1 - I<br>Index-4 Blank<br>R-1 - R-9<br>R-10 Blank. | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| 5-18<br>*Zero in this c                                                                                                                                                                                                                                                   | l<br>Diumn indicates an or                           | 5-113 - 5-11<br>riginal page.                                                                                                                     | 17 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                      |                                                       |

<sup>c</sup>Zero in this column indicates an original page.

NAVELEX 0967-464-0010

Reproduction for non-military use of the information or illustrations contained in this publication is not permitted. The policy for military use reproduction is established for the Army in AR 380-5, for the Navy and Marine Corps in OPNAVINST 5510.LB, and for the Air Force in Air Force Regulation 205-1.

#### INSERT LATEST CHANGED PAGES. DESTROY SUPERSEDED PAGES.

## LIST OF EFFECTIVE **PAGES**

| NOTE: | On a changed page. the portion of the text affected by the latest  |

|-------|--------------------------------------------------------------------|

|       | change is indicated by a vertical line in the outer margin of the  |

|       | page. Changer to illustrations are indicated by miniature pointing |

|       | hands. Changer to wiring diagram are Indicated by shaded areas.    |

Dates of issue for original and changed pages are:

Original . . 0 . . 15 Sep 75 Change . . . 1 . . 1 Jul 79

#### TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS 642 CONSISTING OF THE FOLLOWING:

| Page<br><b>No.</b> | # Change<br>No. | Page<br><b>No.</b> | # Change<br>No. | Page<br><b>No.</b> | # Change<br>No. |

|--------------------|-----------------|--------------------|-----------------|--------------------|-----------------|

| Title              | 1               | 5-30 - 5-3         | 34 0            | 6 - 1 ,            | 0               |

| Α                  | 1               | 5-35 - 5-3         | <b>6</b> 1      | 62 Blank           | 0               |

| i - ix             | 0               | 5-37 - 5-4         | 3 0             | 6 - 3 - 6-25       | 0               |

| x Blank            | 0               | 5 - 4 4            | 1               | 6-26               | i               |

| xi                 | 0               | 5-45               | 0               | 6 - 2 7 - 6-44     | 00              |

| 1-0                | 0               | 5-46               | 1               | Index-l -          | Index-3 . O     |

| 1-1 - 1-4          | 0               | 5 - 4 7 - 5 - 5    | i1 0            | Index-4 Bla        | nk 0            |

| 1-5                | i               | 5-52               | 1               | R-1 - R-9 .        | 0               |

| 1-6 - 1-7          | 0               | 5 - 5 3 - 5 - 5    | 5 0             | R-10 Blank .       | 0               |

| 1 - 8              | 1               | 5-56               | 1               |                    |                 |

| 1-9 - 1-25         | 0               | 5-57               | 0               |                    |                 |

| 1-26 Blank         | 0               | 5-58 - 5-6         | 0 1             |                    |                 |

| 2 - 1 - 2 - 3      | 0               | 5-61               | 0               |                    |                 |

| 2-4 Blank          | 0               | 5-62 - 5-6         | 3 1             |                    |                 |

| 3 - 1              | 0               | 5-64 - 5-6         | 6 0             |                    |                 |

| 3-2 Blank          | 0               | 5-67               | 1               |                    |                 |

| 4 - 1 - 4 - 7      | 0               | 5 - 6 8 - 5 - 7    | 3 0             |                    |                 |

| 4-8 Blank          | 0               | 5 - 7 4 - 5 - 7    | 5 1             |                    |                 |

| 5 - 1 - 5 - 2      | 0               | 5-76 - 5-8         | 80 0            |                    |                 |

| 5 - 3 - 5 - 4      | 1               | 5-61 - 5-8         | 85 1            |                    |                 |

| 5-5-5-6            | 0               | 5-86               | 0               |                    |                 |

| 5 - 7 - 5 - 8      | 1               | 5-87 - 5-9         | 2 1             |                    |                 |

| 5-9-5-10           | 0               | 5-93               | 0               |                    |                 |

| 5-11 - 5-12        | 1               | 5-94               | 1               |                    |                 |

| 5 - 1 3            | 0               | 5-95 - 5-2         | LO8 O           |                    |                 |

| 5-14 - 5-15        | 1               | 5-109              | 1               |                    |                 |

| 5-16 - 5-17        | 0               | 5-110 - 5          | -112 0          |                    |                 |

| 5-18               | 1               | 5-113 - 5          | -117 1          |                    |                 |

| 5-19               | 0               | 5-118 - 5          | -119 0          |                    |                 |

| 5-20 - 5-27        | 1               | 5-120              | 1               |                    |                 |

| 5 - 2 8            | 0               | 5-121 - 5          |                 |                    |                 |

| 5-29               | 1               | 5-134 Bla          | nk 0            |                    |                 |

${}^{\#}$  Zero in this column indicates an original page.

Reproduction for non-military use of the information or illustrations contained in this publication is not **per**mitted. The policy for military use reproduction is established for the Army in AR 38C-5, for the Navy and Marine Corps in OPNAVINST 5510.1B, and for the Air Force in Air Force Regulation 205-1.

#### LIST OF EFFECTIVE PAGES

Insert latest changed pages; dispose of superseded pages in accordance with applicable regulations.

NOTE: On o changed page, the portion of the text affected by the latest change is indicated by a vertical line, or other change symbol, in the outer margin of the page. Changes to illustrations ore inducated by miniature pointing hands. Changes to wiring diagrams are indicated by shaded areas.

Total number of pages in this manual is 642 consisting of the tollowing:

| Page<br>No.                                                                         | #Change<br><b>No.</b> | Page<br>No. | #Change<br>No. |

|-------------------------------------------------------------------------------------|-----------------------|-------------|----------------|

| Title                                                                               | 0                     |             |                |

| A                                                                                   | 0                     |             |                |

| i - i x                                                                             | 0                     |             |                |

| x Blank                                                                             | 0                     |             |                |

| xi                                                                                  | 0                     |             |                |

| 1-0                                                                                 | 0                     |             |                |

| l-l - 1-25                                                                          | 0                     |             |                |

| 1-26 Blank                                                                          | 0                     |             |                |

| 2-1-2-3                                                                             | 0                     |             |                |

| 2-4 Blank                                                                           | 0                     |             |                |

| 3-1                                                                                 | 0                     |             |                |

| 3-2 Blank                                                                           | 0                     |             |                |

| 4 - 1 - 4 - 7                                                                       | 0                     |             |                |

| 4-8 Blank                                                                           | 0                     |             |                |

| $5 - 1 - 5 - 133 \dots \dots \dots \dots \dots$                                     | 0                     |             |                |

| 5-134 Blank                                                                         | 0                     |             |                |

| 6-1                                                                                 | 0                     |             |                |

| 6-2 Blank                                                                           | 0                     |             |                |

| 6-3 - 6-440                                                                         | 0                     |             |                |

| Index-1 - Index-3                                                                   | 0                     |             |                |

| Index-4 Blank                                                                       | 0                     |             |                |

| $\mathbf{R} \cdot \mathbf{l} \cdot \mathbf{R} \cdot 9  .  .  .  .  .  .  .  .  .  $ | 0                     |             |                |

0

# Zero in this column indicates an original page

R-10 Blank . . . . . . . . .

## TABLE OF CONTENTS

I.

I.

| Sectior | 1              |                                               | Page         |  |  |  |

|---------|----------------|-----------------------------------------------|--------------|--|--|--|

| LIS     | ST OF          | ILLUSTRATIONS                                 | vii          |  |  |  |

| LIS     | LIST OF TABLES |                                               |              |  |  |  |

| IN      | FROE           | DUCTION                                       | xi           |  |  |  |

|         |                | ER 1. GENERAL<br>RMATION                      |              |  |  |  |

| 1-1     | l.             | Description and<br>Purpose                    | 1-1          |  |  |  |

| 1-2     | 2.             | Purpose and Use                               | . 1-1        |  |  |  |

| 1-6     |                | Physical Description .<br>Leading Particulars | . 1-1        |  |  |  |

|         | 10.            | Leading Particulars                           | . 1-5        |  |  |  |

| 1-1     | 2.             | Capabilities and<br>Limitations               | 1_5          |  |  |  |

| 1-1     | 4.             | Equipment Supplied                            | . 1-8        |  |  |  |

| 1-1     |                | Special Tools and                             |              |  |  |  |

|         |                | Test Equipment                                | 1-8          |  |  |  |

| 1-1     | 18.            | Related Technical<br>Manuals                  | 1.0          |  |  |  |

|         |                |                                               | 1-9          |  |  |  |

| СН      | APTE           | ER 2. INSTALLATION                            |              |  |  |  |

| 2-1     |                | Introduction                                  | 2-1          |  |  |  |

| 2-3     | 8.             | Reference Data                                | . 2-1        |  |  |  |

| I. INS  | TALI           | LATION LOGISTICS                              |              |  |  |  |

| 2-5     |                | Receiving Data                                | 2-1          |  |  |  |

| 2-7     |                | Material Handling                             | . 2-1        |  |  |  |

| 2-9     | ).             | Unloading and                                 | 0.1          |  |  |  |

| 2-1     | 1              | Unpacking                                     | 2-1<br>2-1   |  |  |  |

| 2-1     |                | Building and Other                            | . ~1         |  |  |  |

|         |                | Supporting                                    |              |  |  |  |

|         |                | Structures                                    | 2-1          |  |  |  |

| II. INS | TALL           | ATION PROCEDURES                              |              |  |  |  |

| 2-1     | 5.             | Contstruction                                 |              |  |  |  |

| 0.4     | 7              | Requirements                                  | 2-2          |  |  |  |

| 2-1     | 1.             | Installation Manpower<br>and Manhour          |              |  |  |  |

|         |                | Requirements . ,                              | 2-2          |  |  |  |

| 2-1     | 9.             | Installation                                  | <i>⊷</i> ~ ~ |  |  |  |

|         |                | Sequence                                      | 2-2          |  |  |  |

| 2-2     | 1.             | Tools and Test                                |              |  |  |  |

|         |                | Equipment                                     | 2-2          |  |  |  |

| Sect | ion                  |                                                        | Page       |  |  |  |

|------|----------------------|--------------------------------------------------------|------------|--|--|--|

|      |                      | Pre-Installation<br>Instructions                       | 2-2        |  |  |  |

|      | 2-23.                | Mechanical<br>Installation                             | 2-2        |  |  |  |

|      | 2-24.                | Electrical In-<br>stallation                           | 2-2        |  |  |  |

|      | 2-25.<br>2-26.       | Power Connections                                      | 2-2        |  |  |  |

|      |                      | ER 3. PREPARATION FOR<br>D RESHIPMENT                  |            |  |  |  |

|      | 3-1.                 | Introduction                                           | 3-1        |  |  |  |

| I.   | PREPAR               | ATION FOR USE                                          |            |  |  |  |

| II.  | PREPAR               | ATION FOR RESHIPMENT                                   |            |  |  |  |

|      | 3-4.                 | Special Instructions.                                  | 3-1        |  |  |  |

|      | 3-6.                 | Use of Dehydrating<br>Agent                            | 3-1        |  |  |  |

|      | CHAPTER 4. OPERATION |                                                        |            |  |  |  |

|      | 4-1.                 | Introduction                                           | 4-1        |  |  |  |

| I.   | CONTRO               | OLS AND INDICATORS                                     |            |  |  |  |

|      | 4-3.                 | Controls and<br>Indicators                             | 4-1        |  |  |  |

|      | CHAPTI<br>OPERATI    | ER 5. THEORY OF<br>ION                                 |            |  |  |  |

|      | 5-1.                 | Introduction                                           | 5-1        |  |  |  |

| I.   | FUNCTI<br>OPERATI    | ONAL SYSTEM<br>ION                                     | 5-1        |  |  |  |

|      | 5-4.                 | Processor and Core<br>Memory Overhaul<br>Block Diagram |            |  |  |  |

|      | 5-7.                 | Description<br>Processor Functiona 1<br>Block Diagram  | 5 - 1      |  |  |  |

|      | 5-8.                 | Description                                            | 5-1<br>5-1 |  |  |  |

|      | 5-26.<br>5-53.       | Bus Controller                                         | 5-4<br>5-8 |  |  |  |

|      | 0 00.                | СРО                                                    | 0.0        |  |  |  |

| Section                                 |                                         | Page         | Section   |                                     | Page                |

|-----------------------------------------|-----------------------------------------|--------------|-----------|-------------------------------------|---------------------|

| 5 - 5 6 .                               | Core Memory                             |              | 5-198.    | CDU ATU In ant                      |                     |

| 0 00.                                   | Core Memory<br>Controller               | 5 - 8        | 0 100.    | CPU ALU Input<br>Multiplexer        | 5-31                |

| 5-59.                                   | Autoload                                |              | 5-208.    | CPU ALU Circuit                     | /                   |

| 5-63.                                   | Parallel I/O                            | 5-10         | 5-215.    | CPU Register File                   | 00.                 |

| 5-69.                                   | TlY Controller                          | 5-11         | • = • • • | Circuit                             | 5-32                |

| 5-75.                                   | Modem Controller 1                      | 5-12         | 5-223.    | CPU Carry and Over-                 |                     |

| 5-81.                                   | Block Transfer                          |              |           | flow Circuit                        | 5-34                |

| 5-88.                                   | Adapter                                 | 5-14         | 5-235.    | CPU Emulation                       |                     |

| 5-00.                                   | Mag Tape                                | E 1 1        |           | Instruction Register                | <b>5</b> 0 <b>5</b> |

| 5-89.                                   | Controller                              | 5-14<br>5-14 | 5-250.    | Circuit<br>CPU Address              | 5-35                |

| 5-93.                                   | Printer Controller                      | 5-14         | 5-250.    | Recognition                         | 5-36                |

| 0.00.                                   | (ACOC Group Only).                      | 5-15         | 5-265.    | CPU INFIBUS Access                  | 5-30                |

| 5-99.                                   | Modem Controller 2                      |              |           | Circuit                             | 5-38                |

|                                         | (ACOC Group Only) .                     | 5-15         | 5-282.    | CPU Central Timing                  |                     |

| 5-105.                                  | Program Maintenance                     |              |           | Control Circuit                     | 5-40                |

| F 400                                   | Panel                                   | 5-16         | 5-302.    | Core Memory Con-                    |                     |

| 5-106.                                  | Core Memory                             |              |           | troller A1A3A8                      |                     |

|                                         | Functional Block<br>Diagram Description | 5-16         |           | Command and Page<br>Select Circuit  | 5-42                |

| 5-107.                                  | General                                 | 5-16         | 5-330.    |                                     | J-42                |

| 5-113.                                  |                                         | 5-17         | 0 000.    | troller A1A3A8                      |                     |

| 5-114.                                  | Read/Write Mode                         | 5-18         |           | Address Transfer                    |                     |

| 5 - 1 1 6 .                             | Processor Detail                        |              |           | Circuit                             | 5-47                |

|                                         | Logic Diagram                           | 5 4 0        | 5-335.    |                                     |                     |

| 5-117.                                  | Description                             | 5-18<br>5-18 |           | troller A1A3A8                      |                     |

| 5-118.                                  |                                         | 5 10         |           | Data Transfer<br>Circuit            | 5-48                |

| 0 110.                                  | A1A3A5 Service                          |              | 5-344.    | Autoload A1A3A9                     | 0 10                |

|                                         | Request Selection                       |              |           | Control Circuit                     | 5-49                |

|                                         | and Interrupt                           |              | 5-354.    | Autoload A1A3A9                     |                     |

| F 400                                   | Circuit                                 | 5-19         |           | Address Recognition                 |                     |

| 5-132.                                  | Bus Controller                          |              |           | and ROM Select                      |                     |

|                                         | A1A3A5 Alarm and                        |              | F 250     | Circuit                             | 5-50                |

|                                         | INFIBUS Timing                          | 5-22         | 5-359.    |                                     |                     |

| 5-150.                                  | Circuit<br>CPU Sequence                 | J-22         |           | INFIBUS Access<br>Circuit           | 5-51                |

| 0 1001                                  | Register and                            |              | 5-370.    | Autoload A1A3A9                     | 001                 |

|                                         | Control Storage                         |              |           | ROM and Data                        |                     |

|                                         | Circuit                                 | 5-26         |           | Circuit                             | 5-53                |

| 5-157.                                  | CPU Microcode                           |              | 5-384.    | Parallel I/O                        |                     |

| 5-167.                                  | Register Circuit                        | 5-27         |           | A1A3A10 Address                     |                     |

| 5-177.                                  | CPU Control Circuit                     | 5-28         |           | Receivers and                       | 5-55                |

| $\mathbf{J}^{-1}\mathbf{I}\mathbf{I}$ . |                                         | 5-28         | 5-396.    | Recognition Circuit<br>Parallel I/O | 0.00                |

| 5-181.                                  | Register Circuit<br>CPU Transmit        |              |           | A1A3A10                             |                     |

| 5 101.                                  | Register Circuit                        | 5 - 2 9      |           | INFIBUS                             |                     |

| 5-192.                                  | CPU Address                             |              |           | Access                              | 5 E 7               |

|                                         | Register Circuit                        | 5-30         |           | Circuit                             | 5-57                |

|                                         |                                         |              |           |                                     |                     |

| Section |                                                             | Page   | Section          | Page                                                            |

|---------|-------------------------------------------------------------|--------|------------------|-----------------------------------------------------------------|

| 5-404.  | Parallel I/O<br>AlA3Al0 Data Input<br>and Selector Circuit. | 5-58   | 5-581.           | Mag Tape Controller<br>Data Output and<br>Control Register      |

| 5-412.  | Parallel I/O Data<br>Output and Control                     | . 5-56 | 5-595.           | Circuit 5-84<br>Mag Tape Controller                             |

| 5-423.  | Register Circuit<br>Parallel I/O Read/                      | 5-59   | 5 000            | Read/Write Control<br>Status Circuit 5-87                       |

| 5-438.  | Write Control<br>Status Circuit<br>Serial I/O Control       | 5-62   | 5-609.<br>5-612. | I/O Controller<br>Clock Circuit 5-88<br>I/O Controller          |

|         | Group Address<br>Recognition                                |        |                  | Address Recognition,<br>Done, and Reset                         |

| 5-457.  | Circuit                                                     | 5-63   | 5-625.           | Circuit 5-88<br>I/O Controller<br>Data Circuit 5-90             |

| 5-469.  | Access Circuit<br>Serial I/O Control                        | 5-67   | 5-632.           | I/O Controller<br>Interface Circuit 5-92                        |

|         | Group Clock<br>Generator<br>Circuit                         | 5-68   | 5-638.           | I/O Controller<br>INFIBUS Access<br>Logic Circuit 5-93          |

| 5-476.  | Serial I/O Control<br>Group Control                         | 5-00   | 5-648.           | Program Maintenance<br>Panel Address/                           |

| 5-483.  | Register Circuit<br>Serial I/O Control<br>Group Data        | 5-69   |                  | Data Switch Iden-<br>tification, Multi-<br>plexers, and LED     |

| 5-501.  | Selector/Control<br>Circuit<br>Serial I/O Control           | 5-69   | 5-658.           | Circuit 5-97<br>Program Maintenance<br>Panel CPU Register       |

| 0.0011  | Group Asynchronous<br>Data Transfer                         |        | 5-661.           | Selection Circuit 5-100<br>Program Maintenance                  |

| 5-521.  | Control Circuit<br>Block Transfer<br>Adapter A1A3A13        | 5-71   |                  | Panel Address<br>Multiplexer, Bus<br>Driver Receiver,           |

| 5-540.  | Control Circuit<br>Block Transfer<br>Adapter A1A3A13        | 5-73   | 5-667.           | and Recognition<br>Circuit 5-101                                |

|         | Address , Data ,<br>and Block Length                        |        | 5-007.           | Program Maintenance<br>Panel Data Multi-<br>plexer and Bus      |

| 5-551.  | Circuit                                                     | 5-78   | 5 070            | Driver Receiver<br>Circuit 5-102                                |

|         | Receivers and<br>Recognition<br>Circuit                     | 5-80   | 5-676.           | Program Maintenance<br>Panel Switch Flip-<br>Flop and Single    |

| 5-563.  | Mag Tape Controller<br>AlA3A14 INFIBUS                      |        | 5-688.           | Action Discrimina-<br>tion Circuit 5-104<br>Program Maintenance |

| 5-573.  | Access Circuit<br>Mag Tape Controller<br>AlA3A14 Data Input | 5-81   |                  | Panel<br>Miscellaneous<br>Control                               |

|         | and Selector Circuit.                                       | 5-83   |                  | Circuit 5-105                                                   |

| Sect | ion_             |                                                              | Page           | Section                    |                                                       | Page           |

|------|------------------|--------------------------------------------------------------|----------------|----------------------------|-------------------------------------------------------|----------------|

|      | 5-696.           | Program Maintenance<br>Panel State Gener-<br>ation and Micro |                | 5-767.<br>5-768.<br>5-769. | PCB (80331260-000).<br>SWB (90331080-000).<br>CM MIA  | 5-125<br>5-125 |

|      | 5-716.           | Operations Circuit<br>Program Maintenance                    | 5-106          | 5-770.                     | (80332060-000)<br>CM MIB                              | 5-125          |

|      |                  | Panel INFIBUS Access<br>Logic Circuit                        | 5-112          | 5-771.                     | (80331070-000)<br>CM MBA                              | 5-125          |

|      | 5-726.           | Core Memory Detail<br>Logic Diagram                          |                | 5-772.                     | (80331090-000)<br>CM MMA                              | 5-126          |

|      | 5-728.           | Description                                                  | 5-115          | 5-773.                     | (80331110-000)<br>CM MSA                              | 5-126          |

|      | 5-737.           | Logic Circuit<br>Address Register,                           | 5-116          | 5-774.                     | (80331080-000)<br>Integrated Circuit                  | 5-126          |

|      | 0 101.           | Decoding, Switching,<br>and Control and                      |                | 5-776.                     | Descriptions<br>N8202N, 10-Bit                        | 5-126          |

|      |                  | Buffer Logic<br>Circuit                                      | 5-117          | 5-777.                     | Buffer Register<br>N8203N, 10-Bit                     | 5-126          |

|      | 5-742.           | Sense, Inhibit,<br>and Data Circuit                          |                | 5-778.                     | Buffer Register<br>N8235N, 2-Input,                   | 5-127          |

| II.  | FUNCTIO          | ONAL OPERATION OF                                            | 5-115          | 5-776.                     | 4-Bit Digital<br>Multiplexer                          | 5-127          |

| 11.  |                  | ONIC CIRCUITS                                                |                | 5-779.                     | N8264N, 3-Input,<br>J-Bit Digital                     | J-127          |

|      | 5-749.<br>5-752. | General PC Card Description .                                | 5-121<br>5-121 | 5-780.                     | Multiplexer N8266B, Z-Input,                          | 5-127          |

|      | 5-756.           | Core Memory<br>Controller                                    |                |                            | 4-Bit Digital<br>Multiplexer                          | 5-127          |

|      | 5-757.           | (80331010-000) Autoload                                      |                | 5-781.                     | P3205, High Speed<br>1 Cut of 8 Binary                |                |

|      | 5-758.           | (80331150-000)<br>Parallel I/O                               |                | 5-782.                     | Decoder                                               | 5-127          |

|      | 5-759.           | (80331180-000)<br>TTY Controller                             | 5-123          | 5-783.                     | 6-Bit Latch SN7442N, FCD to                           | 5-127          |

|      | 5-760.           | (80331140-000)<br>Modem Controller 1                         | 5-123          | 5-784.                     | Decimal Decoder.<br>SN7442A Divide By                 | 5-128          |

|      | 5-761.           | (80331210-000) Block Transfer                                | 5-123          | 5-785.                     | 2, 8 or 16 Bi-<br>nary Counter<br>SN7496, 5-Bit Shift | 5-128          |

|      | 5 709            | Adapter<br>(80331120-000)                                    | 5-123          | 5-785.<br>5-786.           | Register                                              | 5-128          |

|      | 5-762.           | Mag Tape Controller<br>(80331130-000)                        | 5-124          | 5-780.                     | Bistable Latches<br>SN74138N, 3 Line                  | 5-128          |

|      | 5-763.           | I/0 Controller<br>(80330090-000)                             | 5-124          | J-101.                     | to-8 Line Decoder,:                                   | 5- 129         |

|      | 5-764.           | Printer Controller<br>(80331280-000)                         | 5-124          | 5-788.                     | Demultiplexer<br>SN7445, BCD-                         | J- 129         |

|      | 5-765.           | Modem Controller 2<br>(80331190-000)                         | 5-124          |                            | to-Decimal<br>Decoder/                                | r 100          |

|      | 5-766.           | PBI (80331250-000)                                           | 5-125          |                            | Driver                                                | 5-129          |

| Section_ |                                                            | Page           | Section                                                                                       | Page           |

|----------|------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------|----------------|

| 5-789.   | SN74150P, Data<br>Selector/Multi-                          |                | 5-804. SN74198N, 8-Bit<br>Shift Register                                                      | 5-133          |

| 5-790.   | plexer                                                     | 5-129          | 5-805. SN75453, Duel<br>Peripheral<br>Positive-or                                             |                |

| 5-791.   | plexer                                                     | 5-129          | Driver                                                                                        | 5-133          |

|          | Line-to- 1 Line<br>Data Selectors,'<br>Multiplexers        | 5-129          | Differential Line<br>Driver<br>5-807. U7B961559X Dual                                         | 5-133          |

| 5-792.   | SN74154N, 4 Line-<br>to-16 Line De-                        | 5-125          | Differential Line                                                                             | 5-133          |

|          | coders/Demulti-<br>plexers                                 | 5-129          | III. FUNCTIONAL OPERATION OF                                                                  |                |

| 5-793.   | SÑ74157N, Quadruple<br>2 Line-to 1 Line<br>Data Selectors/ |                | MECHANICAL ASSEMBLIES<br>(NOT APPLICABLE)                                                     |                |

| 5-794.   | Multiplexers                                               | 5-129          | CHAPTER 6. MAINTENANCE                                                                        |                |

| 5-795.   | nous 4-Bit Counter .<br>SN74163N, Synchro-                 | 5-129          | 6-3. Maintenance                                                                              | 6-1            |

| 5-796.   | nous 4-Bit Counter .<br>SN74170N, 4-By-4<br>Register File  | 5-130<br>5-130 | 6-6. Use of Test                                                                              | 6 - 1<br>6 - 1 |

| 5-797.   | SN74174N, HEX<br>D-Type Flip-Flops                         | 0 100          | I. ORGANIZATIONAL AND                                                                         | 0 1            |

| 5-798.   | With Clear                                                 | 5-130          | INTERMEDIATE MAINTENANCE                                                                      |                |

|          | ruple D-Type<br>Flip-Flops With<br>Clear                   | 5-131          | 6-9. Maintenance Sup-                                                                         | 6-3<br>6-3     |

| 5-799.   | SN74178 4-Bit<br>Parallel Access                           | 5-151          | 6-11. Performance Test                                                                        | 6-3            |

| 5-800.   | Shift Register<br>SN74181, Arith-<br>metic Logic Unit/     | 5-131          | 6-13. Processor and<br>Core Memory<br>Performance Test                                        |                |

| 5-801.   | Function Generator<br>SN74182N, Look-<br>Ahead Carry       | 5-131          | Tables (Excluding<br>Autoloader), Par-<br>allel I/O, Modem                                    |                |

| 5-802.   | Generator                                                  | 5-131          | Controller, and<br>I/O Controller                                                             | 6-6            |

|          | nous Up/Down<br>Counter With Up/<br>Down Count Mode        |                |                                                                                               | 6-26           |

| 5-803.   | Down Count Mode<br>Control                                 | 5-132          | <ul> <li>6-18. Parallel I/O Per-<br/>formance Test</li> <li>6-19. Modem Controller</li> </ul> | 6-26           |

|          | Presettable Binary<br>Counter/Latches                      | 5-132          | Performance                                                                                   | 6-26           |

|          |                                                            |                |                                                                                               |                |

| Sec | tion      |                                         | Page | Section |                                    | Page  |

|-----|-----------|-----------------------------------------|------|---------|------------------------------------|-------|

|     | 6-20.     | I/O Controller<br>(Switch Group         |      | 6-48.   | CM MIA PC Card<br>Component Per-   |       |

|     |           | Only) Perform -                         | 0.00 | 0.50    | formance Test                      | 6-156 |

|     | 6-21.     | ance Test                               | 6-26 | 6-50.   | CM MIB PC Card                     |       |

|     | 0-21.     | Voltage Require-<br>ments and Sources   | 6-26 |         | Component Per-<br>formance Test    | 6-156 |

|     | 6-23.     | Alignment                               | 6-26 | 6-52.   | CM MSA PC Card                     | 0-130 |

|     | 6-25.     | Test Error Printouts                    | 6-33 | 0 02.   | Component Per-                     |       |

|     | 6-27.     | Processor Interrupt                     | 0.00 |         | formance Test                      | 6-180 |

|     | • • • • • | Test Error                              |      | 6-54.   | CM MBA PC Card                     |       |

|     |           | Printouts                               | 6-33 |         | Component Per-                     |       |

|     | 6-28.     | LF Clock and                            |      |         | formance Test                      | 6-180 |

|     |           | Power Fail Test                         |      | 6-56.   | CM MMA PC Card                     |       |

|     |           | Error Printouts                         | 6-35 |         | Component Per-                     |       |

|     | 6-29.     | Program Mainten-                        |      |         | formance Test                      | 6-211 |

|     |           | ance Panel Test                         |      | 6-58.   | PCB PC Card Com-                   |       |

|     |           | Error Printouts                         | 6-36 |         | ponent Perform-                    | 0.014 |

|     | 6-30.     | TTY Test Error                          | 0.07 | 0.00    | ance Test                          | 6-211 |

|     | 6 91      | Printouts                               | 6-37 | 6-60.   | PBI PC Card Com-                   |       |

|     | 6-31.     | Mag Tape Controller<br>(BTA) Test Error |      |         | ponent Perform-<br>ance Test       | 6-211 |

|     |           | Printouts                               | 6-39 | 6-62.   | TTY Controller PC                  | 0-211 |

| II. | CDECIAI   |                                         |      |         | Card Component<br>Performance Test | 6-266 |

| 11. | SPECIAL   | . MAINTENANCE                           |      | 6-64.   | Mag Tape Controller                | 0-200 |

|     | 6-32.     | General                                 | 6-41 | 0-04.   | PC Card Compon-                    |       |

|     | 6-34.     | Component Parts                         | 0 41 |         | ent Performance                    |       |

|     | 0 0 1.    | Identification                          | 6-41 |         | Test                               | 6-285 |

|     | 6-36.     | Component Per-                          |      | 6-66.   | Block Transfer                     |       |

|     |           | formance Test                           |      |         | Adapter PC Card                    |       |

|     |           | Tables                                  | 6-41 |         | Component Per-                     |       |

|     | 6-38.     | Autoload PC Card                        |      |         | formance Test                      | 6-307 |

|     |           | Component Per-                          |      | 6-68.   | I/O Controller PC                  |       |

|     |           | formance Test                           | 6-41 |         | Card Component                     |       |

|     | 6-40.     | Bus Controller PC                       |      |         | Performance Test                   |       |

|     |           | Card Component                          |      |         | (Switch Group                      | 6 220 |

|     | 0.40      | Performance Test                        | 6-58 | 0.70    | Only) $\ldots$ $\ldots$ $\ldots$   | 6-329 |

|     | 6-42.     | CPA PC Card Com-                        |      | 6-70.   | Parallel I/O PC                    |       |

|     |           | ponent Performance                      | 0 50 |         | Card Component<br>Performance Test | 6-329 |

|     | 6-44.     | Test                                    | 6-58 | 6-71.   | Modem Controller                   | 0-323 |

|     | 0-44.     | ponent Performance                      |      | 0-71.   | 1 PC Card Com-                     |       |

|     |           | Test                                    | 6-99 |         | ponent Perform-                    |       |

|     | 6-46.     | Core Memory Con-                        | 0.00 |         | ance Test                          | 6-351 |

|     | 0 10.     | troller PC Card                         |      | 6-73.   | Printer Controller PC              |       |

|     |           | Component                               |      |         | Card Component                     |       |

|     |           | Performance                             |      |         | Performance Test                   |       |

|     |           | Test                                    | 6-99 |         | (ACOC Group Only).                 | 6-351 |

|     |           |                                         |      |         |                                    |       |

## TABLE OF CONTENTS (cont)

| Section | Title                                           | Page    | Section                | Title           | Page    |

|---------|-------------------------------------------------|---------|------------------------|-----------------|---------|

| 6-75.   | Modem Controller<br>2 PC Card<br>Component Per- |         | III. PERFORM<br>CHECKS | IANCE TEST<br>5 | . 6-433 |

|         | formance Test                                   |         | 6-90.                  | General         | 6-433   |

|         | (ACOC Group                                     |         | 6-92.                  | Preliminary     |         |

|         | Only) $\ldots$ $\ldots$ $\ldots$                | . 6-410 |                        | Instruction     | . 6-433 |

| 6-77.   | Repair and Re-                                  |         | 6-94.                  | Test Checks     | . 6-433 |

|         | placement                                       | . 6-411 | 6-96.                  | Restoring Core  |         |

| 6-79.   | Repair                                          |         |                        | Memory          | . 6-440 |

| 6-85.   | Replacement                                     |         | ALPHAI                 | BETICAL INDEX   | INDEX-l |

| 6-88.   | Testing                                         |         | CROSS I                | REFERENCE INDEX | R-l     |

## LIST OF ILLUSTRATIONS

| Number  |                                         | Page | Number | Page                                        |

|---------|-----------------------------------------|------|--------|---------------------------------------------|

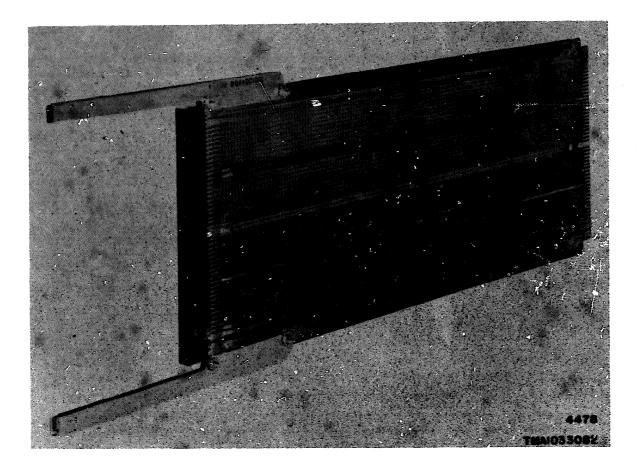

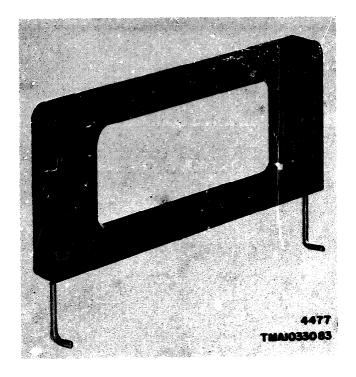

| 1 - 1 . | Processor and Core<br>Memory            | 1-0  | 1-9.   | PC Card Extender,<br>Part No. 715092-l 1-21 |

| 1-2.    | Processor and Core                      |      | 1-10.  | PC Card Extender,<br>Part No. 715138-1 1-22 |

|         | Memory Block<br>Diagram                 | 1-2  | 1-11.  |                                             |

| 1-3.    | Processor, Interior<br>View             | 1-3  | 1-12.  | Part No. 80331730 1-23<br>PC Card Extender. |

| 1-4.    | Core Memory, Interior                   |      |        | Part No. 80331740-000. 1-24                 |

| 1-5.    | View                                    | 1-4  | 1-13.  | Switch Interface Tester<br>Part No.         |

| 1-6.    | Part No. 3916 PC Card Extender.         | 1-17 |        | 90331059-000 1-25                           |

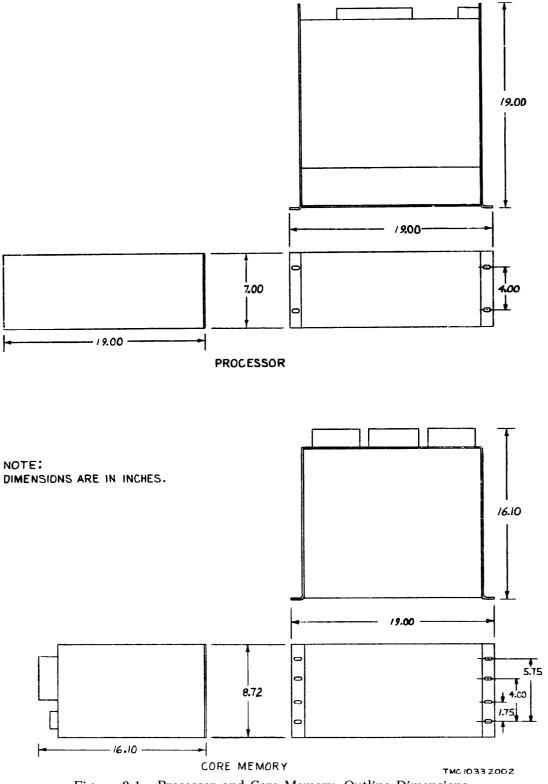

|         | Part No. 7970                           | 1-18 | 2-1.   | Processor and Core                          |

| 1-7.    | PC Card Extractor,<br>Part No. 7971     | 1-19 |        | Memory, Outline<br>Dimensions 2-3           |

| 1-8.    | PC Card Extractor,<br>Part No. 713183-1 | 1 20 | 4 1    |                                             |

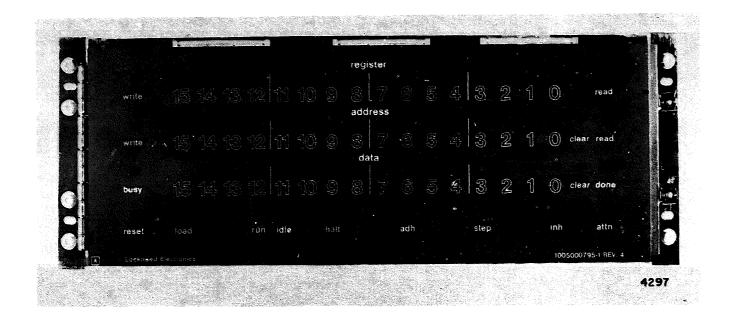

|         | Fait INU. /13103-1                      | 1-20 | 4-1.   | Controls and Indicators 4-2                 |

## LIST OF TABLES

| Number       | Title                                          | Page       |

|--------------|------------------------------------------------|------------|

| 1-1.<br>1-2. | Leading Particular<br>Capabilities and         |            |

| 1-3.         | Limitations                                    | 1-6<br>1 0 |

| 1-3.<br>1-4. | Test Equipment List                            |            |

| 1-5.         | Related Technical<br>Manuals                   |            |

|              |                                                |            |

| 4-1.         | Controls and Indicators                        | 4-1        |

| 5-1.         | Integrated Circuit                             |            |

|              | Descriptions                                   | 5-121      |

| 6-1.         | Maintenance Support                            |            |

|              | Equipment                                      | 6-4        |

| 6-2.         | Performance Test for                           |            |

|              | CPA, CPB, and<br>Bus Controller                | 6-7        |

| 6-3.         | Performance Test for CPA,                      | 0-1        |

| 0 01         | CPB, and Bus Con-                              |            |

|              | troller Interrupt                              | 6-8        |

| 6-4.         | Performance Test for                           |            |

|              | Core Memory and Core                           | 0 11       |

| 6-5.         | Memory Controller<br>Performance Test for CPA, | 0-11       |

| 0 0.         | CPB, PBI, PCB and                              |            |

|              | Program Maintenance                            |            |

|              | Panel                                          | 6-13       |

| 6-6.         | Performance Test for                           |            |

|              | Program Maintenance                            | 0.15       |

| 6-7.         | Panel, PBI and PCB<br>Performance Test for     | 0-10       |

| 0-7.         | TTY Controller and                             |            |

|              | Printer Controller                             | 6-20       |

| 6-8.         | Performance Test for                           |            |

|              | Mag Tape Controller                            |            |

| 6 0          | and BTA                                        | 6-22       |

| 6-9.         | DC Voltage Require-<br>ments and Sources       | 6-27       |

| 6-10.        | Processor Interrupt Test                       | 0-21       |

|              | Number Definitions                             | 6-33       |

| 6-11.        | Processor Interrupt Test                       |            |

| 0 1 9        | Error Definitions                              | 6-34       |

| 6-12.        | LF Clock and Power<br>Fail Test Number         |            |

|              | Definitions.                                   | 6-35       |

| 6-13.        | LF Clock and Power                             |            |

|              | Fail Test Error                                |            |

|              | Definitions                                    | 6-35       |

| Number | Title                                               | Page  |

|--------|-----------------------------------------------------|-------|

| 6-14.  | Program Maintenance<br>Panel Test Number            | 0.00  |

| 6-15.  | Definitions Program Maintenance<br>Panel Test Error | 6-36  |

| 6-16.  | Definitions                                         | 6-37  |

| 6-17.  | Definitions                                         | 6-38  |

|        | Definitions.                                        | 6-38  |

| 6-18.  | Mag Tape Controller<br>(BTA) Test Number            |       |

| 6-19.  | Definitions                                         | 6-39  |

|        | (BTA) Test Error<br>Definitions                     | 6-39  |

| 6-20.  | Autoload PC Card<br>A1A3A9, Performance             |       |

| 6-21.  | Test Bus Controller PC Card                         | 6-42  |

|        | A1A3A5, Performance<br>Test                         | 6-59  |

| 6-22.  | CPA PC Card A1A3A7,<br>Performance Test             | 6-72  |

| 6-23.  | CPB PC Card A1A3A6,<br>Performance Test             | 6-100 |

| 6-24.  | Core Memory Controller                              | 0-100 |

|        | PC Card A1A3A8,<br>Performance Test                 | 6-136 |

| 6-25.  | CM MIA PC Card<br>A1A8A1, Performance               |       |

| 6-26.  | Test                                                | 6-157 |

|        | A1A8A1, Performance<br>Test                         | 6-169 |

| 6-27.  |                                                     |       |

|        | (ACOC Group), and A1A8A3A3, A1A8A4A3,               |       |

|        | A1A8ASA3, A1A8A6A3<br>(Switch Group), Per-          |       |

| 6-28.  | formance Test                                       | 6-182 |

| 0-20.  | A1A8A3A1, A1A8A4A1,                                 |       |

|        | A1A8ASA1 (ACOC<br>Group), and A1A8A3A1,             |       |

|        | A1A8A4A1, A1A8A5A1,<br>A1A8A6A1 (Switch Group)      |       |

|        | Performance Test                                    | 6-199 |

## LIST OF TABLES (cont)

| Number | Title                                                | _Page _ | Number | Title                                                          | Page    |

|--------|------------------------------------------------------|---------|--------|----------------------------------------------------------------|---------|

| 6-29.  | CM MMA PC Card<br>A1A8A3A2, A1A8A4A2,                |         | 6-33.  | Mag Tape Controller<br>PC Card A1A3A14,                        |         |

|        | A1A8A5A2 (ACOC<br>Group), and<br>A1A8A3A2, A1A8A4A2, |         | 6-34.  | Performance Test<br>Block Transfer Adapter<br>PC Card A1A3A13, | 6-286   |

|        | A1A8A6A2 (Switch                                     |         |        | Performance Test                                               | 6-309   |

|        | Group), Performance                                  |         | 6-35.  | I/O Controller PC Card                                         |         |

| 0.00   |                                                      | 6-212   |        | A1A3A15, Performance                                           | 0 0 0 0 |

| 6-30.  | PCB PC Card<br>A1A3A18 (ACOC                         |         | 6 36   | Test                                                           | 6-330   |

|        | Group), A1A3A2 1                                     |         | 0-30.  | A1A3A10 Performance                                            |         |

|        | (Switch Group),                                      | 0.010   | 0.07   | Test                                                           | 6-352   |

| 6-31.  | Performance Test<br>PBI PC Card                      | 6-219   | 6-37.  | Modem Controller 1<br>PC Card A1A3A12,                         |         |

|        | A1A3A17 (ACOC                                        |         |        | Performance Test                                               | 6-372   |

|        | Group), A1A3A20<br>(Switch Group) ,                  |         | 6-38.  | Printer Controller PC<br>Card A1A3A16, Per-                    |         |

|        | Performance Test                                     | 6-246   |        | formance Test                                                  | 6-391   |

| 6-32.  | TTY Controller PC<br>Card A1A3A11,                   |         | 6-39.  | Modem Controller 2<br>PC Card A1A3A17,                         |         |

|        | Performance Test                                     | 6-267   |        | Performance Test                                               | 6-414   |

#### INTRODUCTION

The information in this technical manual pertains to Processor Assembly, STELMA Part No. 90331023-(), and Gore Memory, STELMA Part No. 90331069-(), hereafter referred to as Processor and Core Memory, respectively. Coverage is provided for two versions of the Processor and of the Core Memory: Processor Part No. 90331023-000 and Core Memory Part No. 90331069-600, installed in Data Analysis-Programing Group OL-122/G & (), hereafter referred to as Switch Group; and Processor Part No. 90331023-001 and Core Memory Part No. 90331069-001, installed in Data Analysis-Programing Group OL-123/G & (), hereafter referred to as Area Communications Operations Center (ACOC) Group. Because of the commonality of the two versions, and the fact that existing differences are minor, references in this technical manual to Processor and Core Memory apply to both versions; existing differences are distinguished by reference to the appropriate group (i.e., Switch Processor, Switch Core Memory, ACOC Processor, ACOC Core Memory).

The Processor, operating under program control, initiates real time data processing instructions for the Switch and ACOC Groups. The Core Memory provides word memory for storing Processor operating programs and data base information.

This technical manual, which provides information for operating and maintenance personnel, is divided into six chapters as follows;

Chapter 1, General Information, defines the purpose of the equipment and provides a brief description of, and pertinent data for, the equipment.

Chapter 2, Installation, contains procedures for unpacking and installing the equipment.

Chapter 3, Preparation for Use and Reshipment, provides procedures for initializing the equipment prior to making it operational, and preparing it for reshipment.

Chapter 4, Operation, contains descriptions of all controls and indicators, normal operating procedures and emergency operating procedures.

Chapter 5, Theory of Operation, discusses the functional operation of the equipment and provides descriptions of its electronic circuits.

Chapter 6, Maintenance, contains performance test data, alignment procedures, and servicing information for the equipment.

The following specifications were used in preparation of this manual.

| MIL-M-38798     | Manuals, Technical: Operation Instructions, Maintenance<br>Instructions, Circuit Diagrams, Alignment Procedures, and<br>Installation Planning |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-M-38784     | Technical Manuals: General Requirement for Preparation of                                                                                     |

| MIL-STD-12B     | Abbreviations for Use on Drawings and in Technical Type Publications                                                                          |

| ASA Y32.16-1965 | Electrical and Electronic Reference Designations                                                                                              |

| MIL-P-38790     | Printed Production of Technical Manuals: General Requirements For                                                                             |

#### CHAPTER 1

#### GENERAL INFORMATION

#### 1-1. DESCRIPTION AND PURPOSE.

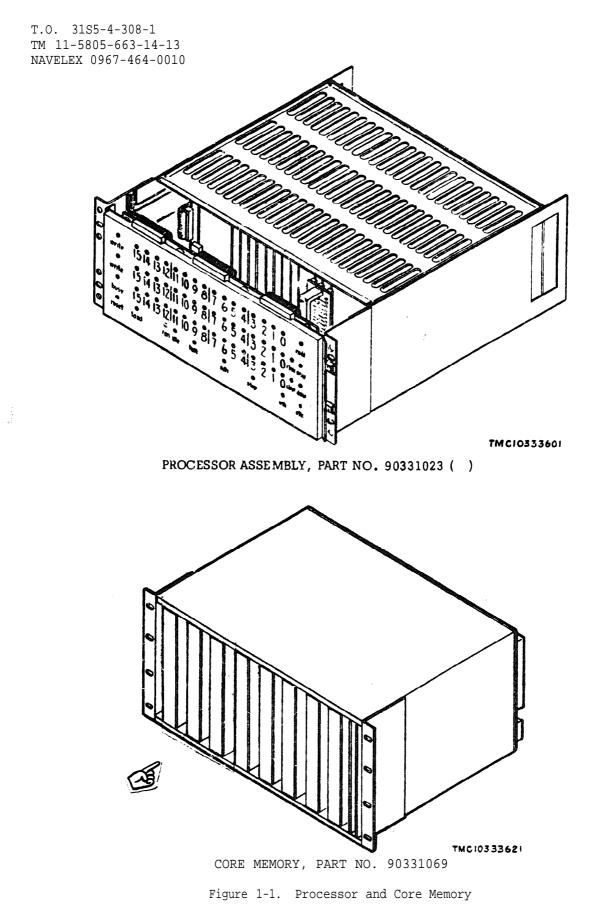

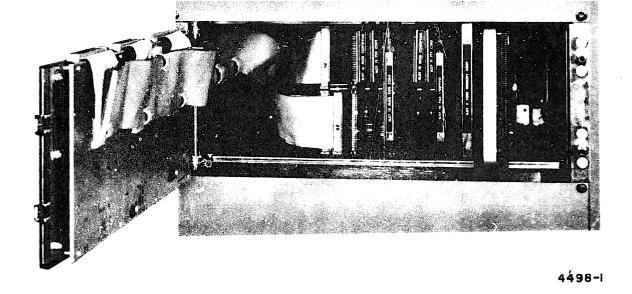

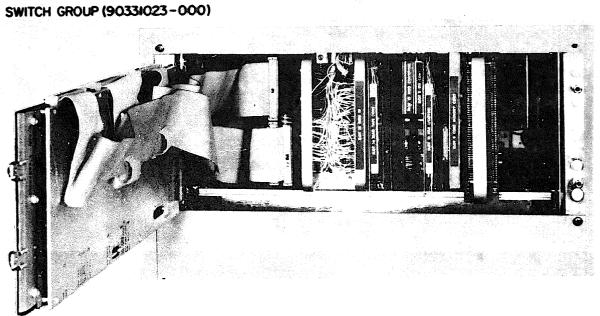

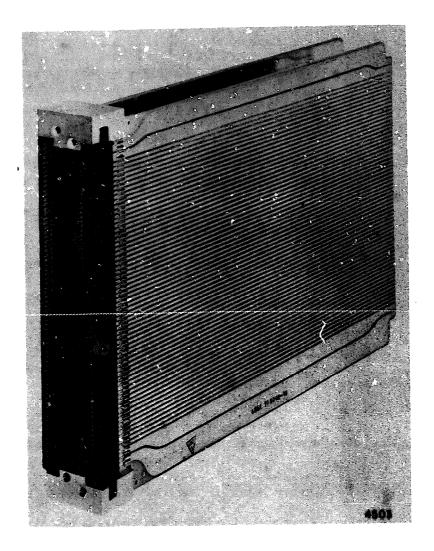

1-2. PURPOSE AND USE. The Processor (see figure 1-1) is a modified general purpose Lockheed Electronics Type SUE\* mini-processor; the Core Memory (sec figure 1-1) is a modified STORE Type 333 Core Memory. Both have been modified for installation in the ACOC Group and Switch Group and to provide the following specific functions required in the Traffic Data Collection System (TDCS).

1-3. Processor Functions.

a. Receive and edit traffic data collection instructions for transmission between Switch and ACOC groups.

b. Receive and edit traffic and call data between Switch and ACOC Groups.

**C.** Send traffic and call data to the appropriate output.

d. Perform other processing as required to satisfy requirements between Switch and ACOC Groups.

e. Select and run programs to perform the processing automatically at the request of the Operator or Executive.

f. Provide for modifying, adding, or deleting programs.

g. Update the System clock or those portions thereof that are provided by software.

h. Provide Operator interrupt and abort capabilities and automatic interrupt capabilities for processing programs.

i. Service all input and output requests.

\*System Use- Engineered

**j.** Respond to Operator and Switch or ACOC Groups requests for service.

k. Perform other control functions as required.

1-4. Core Memory Functions.

a. Store traffic data collection instructions for transmission and transmits them when requested.

b. Store special request traffic data collection (short) reports until the printer is available.

**C.** Transmit stored special request traffic data collection (short) reports to printer when requested.

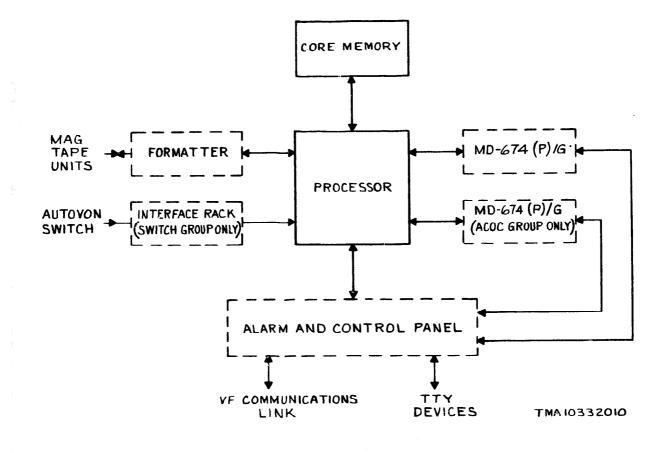

1-5. The functional relationship of the Processor and Core Memory to each other and to the Switch and ACOC Groups is shown in figure 1-2.

1-6. PHYSICAL DESCRIPTION. The Processor (figure 1-3) and Core Memory (figure 1-4) as shown in figure 1-1 are housed in rectangular cases that are 19 inch standard rack mounted into the Switch and ACOC Groups. Vertical cooling is provided to the Processor and Core Memory by rack fans. The Core Memory is also horizontally cooled by three self contained exhaust fans to meet its cooling requirements. The Processor and Core Memory are interconnected by a single cable.

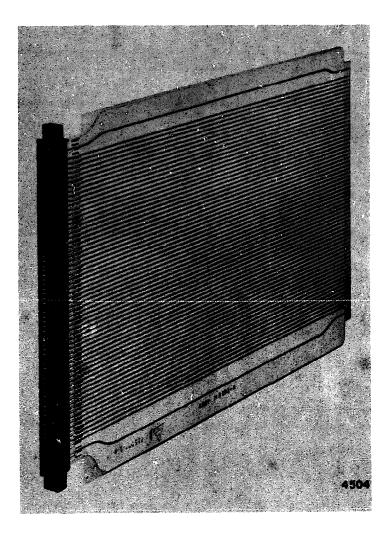

1-7. The Switch Processor contains 17 PC cards and the ACOC Processor contains 14 PC cards which collectively per-form the processing functions. Tire cards are inserted into an INPIBUS, a time shared data highway used as a communication

Figure 1-2. Processor and Core Memory Block Diagram

Figure 1-3. Processor, Interior View

Acoc GROUP (90331023-001)

4495-1

4310-2

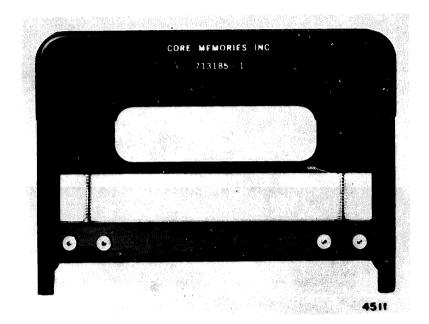

Figure 1-4. Core Memory Interior View

link between the central processor and all other peripheral devices associated with the processor. External and other internal signals are connected to the other side of some PC cards by connectors. Mounted on the front of the Processor is a Program Maintenance Panel covered by a translucent RFI bezel. Touch-sensitive switches and light-emitting diode (LED) indicators on the panel enable a programmer or maintenance technician to check the operation of the Processor by manually entering instructions and observing readouts on the indicators. The panel is connected to the Processor by three ribbon cables.

1-8. The Switch Core Memory contains two logic control PC cards and eight magnetic core memory modules that provide

8,192 words of storage each. Thus, the Sketch Core Memory has a 65,536 word capacity (16-bits per word + 2 parity bits). The ACOC Core Memory has the same capacity as the SSU. Magnetic core memory modules are made up of three PC cards arranged in sandwich fashion and interconnected by means of standard PC board edge-connector. A terminal strip and three connectors are installed on the back cover for Core Memory power and signal interface.

1-9. The reference designation of the Processor is A1A3 and the Core Memory is A1A8. This designation is derived from the reference designation of the Data Processing Assembly A1 which is a part of the Switch and ACOC Groups. The Processor is the third unit and the Core Memory is the eighth unit of this assembly. The second card of the Processor has the reference designation A1A3A2 etc.

1-10. LEADING PARTICULARS .

1-11. Table l-l lists leading particulars and logistical characteristics of the Processor and Core Memory.

1-12. CAPABILITIES AND LIMITATIONS.

1-13. Table 1-2 lists the capabilities and limitations of the Processor and Core Memory.

| ITEM                 | DESCRIPTION                                 |

|----------------------|---------------------------------------------|

| Cooling:             |                                             |

| Processor            | Vertical                                    |

| Core Memory          | Vertical and horizontal                     |

| Dimensions (inches): |                                             |

| Processor            | 7 high by 19 wide by 19 deep                |

| Core Memory          | 8-3/4 high by 18-1/4 wide by 15-3/4<br>deep |

| Power Requirements:  |                                             |

| AC:                  |                                             |

| Processor            | 115 + 10 volt, single phase 50 or 60 Hz     |

Table 1-1. Leading Particulars

## Table 1-1. Leading Particulars (Cont'd)

| ITEM                                | DESCRIPTION                                                                              |

|-------------------------------------|------------------------------------------------------------------------------------------|

| <b>Power</b> Requirements: (Cont'd) |                                                                                          |

| DC:                                 |                                                                                          |

| Processor                           | +5 +2% volts at 30 amperes<br>+15 +1% volts at 1.5 amperes<br>-15 +1% volts at 1 amperes |

| Switch Core Memory                  | +5 +3% volts at 8.0 amperes<br>-15 +2% volts at 5.4 amperes                              |

| ACOC Core Memory                    | +5 +3% volts at 5.6 amperes<br>-15 +2% volts at 4.7 amperes                              |

| Signal Cable Requirements           | 3 twisted pair No. 22 AWG                                                                |

| Storage Environment:                |                                                                                          |

| Temperature                         | -40° to 140°F                                                                            |

| Relative Humidity                   | 90 percent maximum                                                                       |

| Altitude                            | Sea level to 40,000 feet                                                                 |

| Weight (pounds):                    |                                                                                          |

| Processor                           | 42.0                                                                                     |

| Core Memory                         | 46.5                                                                                     |

| Table 1-2. | Capabilities | and | Limitations |

|------------|--------------|-----|-------------|

|------------|--------------|-----|-------------|